Οργάνωση Υπολογιστικών Συστημάτων

Ελένη Λαΐτσου

Ε.ΔΙ.Π.

Μαθησιακά Αποτελέσματα

Το μάθημα εισάγει τους φοιτητές στη δομή και τη λειτουργία ενός σύγχρονου επεξεργαστικού συστήματος και ειδικότερα στις αρχές της διασύνδεσης λογισμικού και υλικού μέσω της αρχιτεκτονικής συνόλου εντολών. Με την επιτυχή ολοκλήρωση του μαθήματος ο φοιτητής / τρια θα είναι σε θέση:

- να κατανοεί τη λειτουργία και την οργάνωση ενός σύγχρονου επεξεργαστή,

- να γνωρίζει τις βασικές αρχές της αρχιτεκτονικής συνόλου εντολών ενός επεξεργαστή (assembly) και να κατανοεί την σχέση μεταξύ της γλώσσας assembly, των γλωσσών προγραμματισμού υψηλού επιπέδου και του επεξεργαστή,

- να μπορεί να προγραμματίζει αλγόριθμους με την χρήση της γλώσσας μηχανής (assembly),

- να κατανοεί την αριθμητική των υπολογιστών τόσο ακεραίων αριθμών όσο και αριθμών κινητής υποδιαστολής,

- να μπορεί να αναλύει την απόδοση ενός επεξεργαστικού συστήματος και να κατανοεί τους παράγοντες από τους οποίους αυτή εξαρτάται,

- να μπορεί να υλοποιεί και να προσομοιώνει έναν προγραμματιζόμενο επεξεργαστή σε γλώσσα περιγραφής υλικού, όπως η Verilog η την VHDL.

Ενδεικτικό Περιεχόμενο Μαθήματος

- Γενική περιγραφή της οργάνωσης ενός Η/Υ

- Εισαγωγή στη συμβολική γλώσσα μηχανής (assembly) με έμφαση στην assembly του επεξεργαστή MIPS

- Υποστήριξη διαδικασιών (procedures) στο υλικό (hardware) ενός Η/Υ

- Εξαιρέσεις και Διακοπές (Exceptions/Interrupts) σε έναν επεξεργαστή.

- Αρχιτεκτονική x86 και σύγκριση αρχιτεκτονικών RISC και CISC.

- Αναπαράσταση αριθμητικών δεδομένων στον Η/Υ. Αναπαράσταση συμπληρώματος ως προς 2 και αριθμητική κινητής υποδιαστολής.

- Αλγόριθμοι εκτέλεσης αριθμητικών πράξεων όπως πρόσθεσης και πολλαπλασιασμού.

- Μετρικές απόδοσης ενός υπολογιστικού συστήματος.

- Μικρο-αρχιτεκτονική επεξεργαστών MIPS.

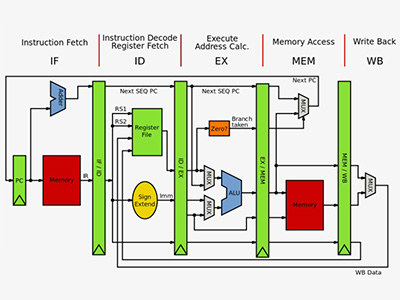

- Υλοποίηση μικρο-αρχιτεκτονικής ενός κύκλου μηχανής. Τμήμα ελέγχου και τμήμα δεδομένων.

- Μικρο-αρχιτεκτονική διοχέτευσης (pipeline). Προβλήματαπου δημιουργεί η διοχέτευση όπωςδομικάλάθη, λάθη δεδομένων και λάθη ελέγχου ( structural, data, controlhazards).

- Ιεραρχία μνήμης και μνήμες cache. Απόδοση συστήματος με ιεραρχία μνήμης.

- Εικονική Μνήμη (Virtual Memory).

- Εισαγωγή στην γλώσσα περιγραφής υλικού Verilog και δημιουργία επεξεργαστικών συστημάτων με την χρήση Verilog ή VHDL.